Assembly and Interconnection Technologies for Sensors for Very High Temperature Applications Jürgen Wilde, Philipp Wagner, Roderich Zeiser, University of Freiburg – IMTEK, Department of Microsystems Engineering

Laboratory for Assembly and Packaging, juergen.wilde@imtek.uni-freiburg.de

#### **Abstract**

This work aims at the development of technologies to assemble, interconnect and protect sensor elements operating in harsh environments up to  $500~\rm C$ . Silicon test-chips were mounted on substrates made of  $Al_2O_3$ , AlN and  $Si_3N_4$  to examine their influence on the sensor. Active metal brazing, glass soldering and ceramic bonding were used as mounting technologies. The stress induced in the chip by the die attachment process was analyzed by optical deformation measurements of the chips as well as by FEM-simulations and by resistance measurements. The mechanical stability of the assemblies was tested with shear-tests before and after 100 hours storage at  $500~\rm C$ . In our study the glass-soldering process on an AlN substrate appeared to be the most suited technology when the reliability of SiC-MEMS is the principal criterion. In a second step an interconnection technique based on fine wire bonding was developed. When metallurgical systems consisting of Pt or Pd are used for the metallization and the wires, these interconnect systems can be stable. Up to date, we could verify the stability after temperature soak at  $500~\rm C$  and during operation at  $300~\rm C$ .

Fig. 1 Pressure sensor in the combustion chamber of a Diesel engine. Image courtesy of Robert Bosch GmbH.

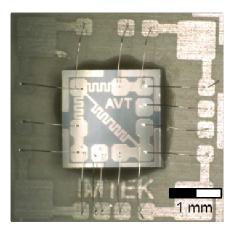

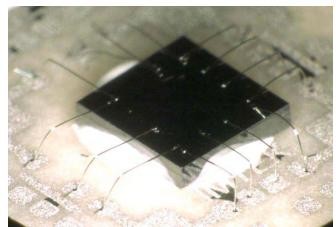

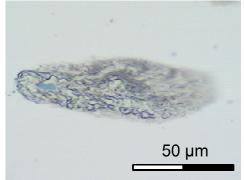

Fig 2 Thin film test sensor assembled with temperature stable technologies up to 600 °C

#### 1. Introduction

In the fields of chemical plants, aeronautical applications and automotive technology there is a strong demand for sensors which can acquire physical or chemical data even in extremely harsh environments. Despite these adverse conditions the measurements must be precise and the sensors must be reliable over long operating times. In the development of combustion engines there has been a strong trend towards the use of sensors in order to monitor the combustion process directly. Such applications comprise diesel engines, gas turbines or fuel cells, where pressures, temperatures or flow rates must be controlled. Depending on the field of use, the sensors must withstand large numbers of temperature- and pressure cycles as well as vibrations over lifespans up to 100,000 hours.

In order to integrate the sensors functionally and structurally into the engines, the transducer element must be mounted, interconnected electrically and protected. These are the principal functions of assembly, interconnection and packaging technology. In the present investigation these technologies are regarded with respect to a pressure sensor to be installed in the combustion chamber of Diesel engines. Fig. 1 shows the possible installation of such a sensor inside the cylinder head of the engine. In order to accomplish the desired pressure sensing function first-of-all a robust sensing element is indispensable. In [1] and [2] pressure sensors were presented, which can operate up to 500 °C. Both sensors are based on silicon carbide (SiC) as the functional material. Contrary to silicon-based semiconductors, which can be operated only up to 250 °C, SiC has the potential for application at significantly higher temperature levels. The functional reason is the wider semiconductor band-gap and the resulting lower intrinsic carrier concentration at elevated temperatures. In addition, significant progress has been achieved in order to harden these materials against very hot and harsh environments [3]. Typically such transducers are fabricated by bulk-micromachining of SiC-wafers [2] as well as by the deposition of SiC-semiconductor

layers on silicon wafers [1]. For the application, besides a robust sensor element, also a highly stable assembly- and packaging technology using matching material systems are required. The materials options for high temperature assemblies are reduced progressively with increasing operating temperatures. Most organic materials will not withstand temperatures beyond 300 °C.

In order to operate SiC-sensors at temperatures above 500  $^{\circ}$ C over long times, new material systems were investigated [4, 5]. For substrates AlN und Si $_3$ N $_4$  can be considered, as their CTE matches well with Si and SiC and thermal-mechanical stresses are reduced. Besides, the mounting technique is of high importance. In [5] a SiC pressure-sensor was mounted using glass. Nevertheless, we have registered few investigations, which assess the influence of thermal stresses on the accuracy and stability of the sensor element.

Wire bonding is a very well-established technology for interconnections. The process is very versatile with respect to geometry, metallurgy and series size. Wire-bonding has already been investigated successfully to contact high-temperature devices [6]. At temperatures up to 600 °C degradation processes like diffusion and metallurgical reactions, oxidation, thermal-mechanical stresses and fatigue and loss of the wire strength will become hazardous. Solutions to these problems can only be found when suitable wire materials and matching pad metallurgies are applied. Au, Pd, Pt and Ni have been proposed as bonding wires in former studies [6, 7, 8]. Except Au these materials have a sufficient strength, even at higher temperatures. Unfortunately they are relatively hard at room temperature. Therefore process optimization is mandatory to avoid chip damage during the bonding. In this paper both the mounting of the sensors and their electrical interconnection will be adressed.

## 2. Mounting of sensor elements

The material chosen as substrate (Table 1) and for die-attachment should match the thermo-mechanical properties of the sensor element to reduce thermally induced stress after the packaging process. Organic adhesives and even polyimides can no longer be used for mounting silicon sensors at operating temperatures above 350 ℃. Soft solders can be used up to 50 K below their melting temperature, which is typically in a range of 210-320 ℃. In this work glass soldering, brazing and ceramic bonding for dieattach of SiC-sensors, technologies which are able to withstand extreme temperatures, are investigated and compared to each other relating to stability and reliability, Table 2.

Table 1 Materials properties of the ceramic substrates

|                                | α in<br>ppm/<br>K | λ in<br>W/mK | E in<br>GPa |

|--------------------------------|-------------------|--------------|-------------|

| Silicon                        | 2.6               | 150          | 161         |

| $Al_2O_3$                      | 7.3               | 24           | 340         |

| AIN                            | 5.2               | 170          | 310         |

| Si <sub>3</sub> N <sub>4</sub> | 3.0               | 70           | 314         |

Data at room temperature, given by the manufacturers and reference [9]

Table 2 High temperature stable die-attachment materials and their properties given by the manufacturers

| Sample   | Material         | CTE<br>α in<br>ppm/K | Process<br>T <sub>PRO</sub><br>in ℃ | Max.<br>use<br>T <sub>MAX</sub> in<br>℃ | Layer<br>thickness<br>d <sub>M</sub> in μm |

|----------|------------------|----------------------|-------------------------------------|-----------------------------------------|--------------------------------------------|

| C-A I    | $Al_2O_3$        | 7.2                  | 150                                 | 1520                                    | 120                                        |

| C-A II   | $Al_2O_3$        | 7.2                  | 370                                 | 1650                                    | 120                                        |

| C-A III  | MgO              | 4.7                  | 20                                  | 1540                                    | 120                                        |

| C-A IV   | SiO <sub>2</sub> | 0.5                  | 300                                 | 1470                                    | 120                                        |

| HT-A     | Siloxane         | NA                   | 250                                 | 650                                     | 50                                         |

| Glass    | Borosilicate     | 3.3                  | 700                                 | 650                                     | 80                                         |

| Braze I  | AgCuTi           | 20                   | 900                                 | 800                                     | 60                                         |

| Braze II | AgTi             | 20                   | 1000                                | 900                                     | 60                                         |

#### **Experimental**

The die-attach techniques, active metal brazing, glass-soldering and ceramic bonding were tested on silicon test-chips with Pt thin films made of standard Si (100) to simulate a high temperature pressure sensor, with a thin SiC-layer [1]. Fig. 2 exhibits a prototype of our thin film stress-sensor. The temperature-stable metallization has an electrical resistivity proportional to the strain. Here it is mounted on a  $Si_3N_4$  substrate and connected with platinum wire bonds to the sensor substrate. Furthermore, the test-chips are mounted on  $Al_2O_3$  and AlN substrates. Table 1 shows the most important material properties of these ceramics in comparison to silicon. Also a finite-element simulation using the software ANSYS was carried out to obtain the mechanical stress in the test-chip after the assembly process. The model of the test-chip was three-dimensional and we used material data given by the manufacturers. For the reference temperature either the process temperature or in the case of glass solder the glass transition temperature was taken.

The evaluated technologies for die-attachment of the test-chip, as well as the respective materials and their properties are shown in Table 2. These comprise the Coefficient of Thermal Expansion (CTE)  $\alpha$ , the process temperature  $T_{PRO}$ , and the maximal operating temperature  $T_{MAX}$ . The ceramic adhesives are denoted as C-A I to C-A IV, HT-A is a siloxane resin. The adhesives were dispensed to the substrate and the test-chips were pick-and-placed with a manipulator. After the mounting the ceramic adhesives and the siloxane were cured at their appropriate temperature  $T_{PRO}$ , according to manufacturers' data. The brazing was done in an argon atmosphere at 900 °C for Braze I and at 1000 °C for Braze II. After the die-attachment process, metallographic sections were made. In Fig. 3 sections of test sensors mounted with Braze II (AgTi) and Braze I (AgCuTi) are presented. The wetting was adequate on all ceramic substrates and only a low amount of voids was observed in the layers. The measured layer thicknesses  $d_M$  which are important for stress analysis are also given in Table 2.

Fig. 3 Micrograph of sections of assemblies with Braze II(left) and Braze I (middle) and C-A I (right)

## Stress induced by die-attachment process

CTE differences of chip, substrate and mounting material lead to thermal stress inside an assembly after the die-attach process. A formula which describes the main influencing factors is given in Eq. 1 [8].

$$\sigma = C \cdot (\alpha_{Sub} - \alpha_{Chip}) \cdot (T_{PRO} - T_R) \cdot \left[ \frac{E_{Sub} \cdot E_M \cdot L_{Chip}}{d_M} \right]^{1/2} \qquad \sigma = \frac{E_{Chip} \cdot t}{2R}$$

Eq. 1: Thermal stress in a chip, induced by the packaging process, with geometric factor C [11]

Eq. 2: Bending stress in a chip, for radius R, thickness t and Young's-Modulus E<sub>Chip</sub> [12]

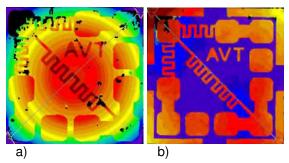

The key parameters for the stress in a chip, induced by the package are: The difference between the process temperature  $T_{PRO}$  and the actual temperature  $T_R$  (room-temperature) the CTEs of substrate  $\alpha_{Sub}$  and chip  $\alpha_{Chip}$ , the Young's Moduli of substrate  $E_{Sub}$  and the mounting material  $E_M$ , the thickness of the die-attach layer  $d_M$  and the size of the chips  $L_{Chip}$  [11]. A relatively simple approach to estimate the bending stress in a chip is to measure the curvature of its surface and to calculate the bending stress with Equation 2 [12]. A white light interferometer (WLI) was used to measure the inverse bending radius  $R^{-1}$  of the test-chip surface. In Fig. 4 topographies of two test-assemblies on  $Al_2O_3$  at room temperature and typical warping data on a diagonal path over the chip are presented. The chip-surface mounted with glass-solder shows a strong curvature. The test-chip attached by siloxane resin stays almost perfectly planar.

Fig. 4 WLI measurement of the chip warping at 20 °C: a) Glass-solder (2  $\mu$ m), b) Siloxane resin

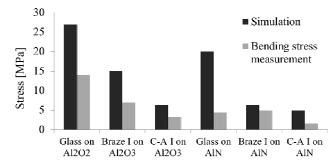

Fig. 5 Comparison of simulation results and bending stress computed from the measured warping of the

$(0.1 \mu m)$ ; both on Al<sub>2</sub>O<sub>3</sub>

test-chip, using Eq.2

From the measured warping of the chips along a path through the middle of the chip the bending radii were calculated and the bending stress was computed. Fig. 5 presents the results for the bending stress of the different die-attach technologies, investigated in this work. For the test-chips soldered with glass on  $Al_2O_3$ , the highest bending stress of 14 MPa was measured. In some test-chips cracks in the surface due to the high stress values were observed. For the chips on  $Si_3N_4$  and AIN, the bending stress was 4 MPa. Brazing induces bending stress in the range of 6 MPa. Very low stress was found for the siloxane resin HT-A. Ceramic adhesives induce lower bending stresses than brazes. C-A I and C-A II had average values of 2 and 3 MPa. For C-A I a high dependence of the stress on the sensor substrate was observed.

FEM-simulations of the assembly processes were conducted to compare the results for the stress in the chip with the bending stress obtained from Eq. 2. The deformation fields are similar to the ones from the WLI. The simulated and the measured stresses correlated well, but the simulation data are generally higher. We expect that the main reason is that the simulation reveals the total stress while the warping measurement makes only the bending stress available. When we compare the bending stress and that from Equation 1, this yields a geometry factor C = 0.0028 for the considered assemblies.

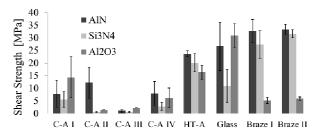

## Stability of the Assembly

The stability of the die-attachments was examined using shear tests and analysis of the fracture surface. In the case of ceramic attachment materials, the fracture mode was adhesive fracture, both on the Si-side and on the substrate side. Such assemblies consistently showed low shear strengths around 4 MPa, while for C-A I and C-A IV a mixed fracture behavior led to strength values of 8 MPa, Fig. 6. The glass-soldered and brazed assemblies showed high shear strengths. So in most cases the chip broke instead of being lifted off, due to a good interface adhesion. For the brazed chips on  $Al_2O_3$ -substrates and for glass soldered chips on  $Si_3N_4$  lower shear strengths were measured. Consistently high shear strengths around 20 MPa were observed for the test-chips mounted with HT-A on all three substrates.

Storage at 500 °C for 100 h in air resulted in degradation of most of the test-assemblies, Fig. 7. The shear strength of the siloxane resin (HT-A) and the adhesion of C-A IV (SiO<sub>2</sub>) were drastically reduced after the aging. On Al<sub>2</sub>O<sub>3</sub>, the shear strength was degraded for C-A I, but on the other substrates it was slightly increased. C-A III has not been age-tested due to its poor initial performance. The adhesion of the brazed samples was reduced by 60 percent after aging. The test-chips soldered with the borosilicate-glass showed nearly the same strength as without aging, except that the chips on Si<sub>3</sub>N<sub>4</sub> even improved by 50 percent. All of these results are summarized in Fig. 6, directly after the assembly process, and in Fig. 7 after storage of 100 h at 500 °C.

Fig. 6 Shear-test results for the die-attachment technologies directly after assembly process

Fig. 7 Shear-test results for the die-attachment technologies after storage for 100 h in air at 500  $^{\circ}\text{C}$

# 3. Wire bonding for high temperatures

## **Experimental**

Based on the considerations above, Pt and Pd were selected as the principal materials of the investigation. Also, as the coefficients of thermal expansion (CTE) of such wires are similar to those of the components, we expected that thermal cycles with  $\Delta T$  of up to 600 K could be tolerated better, Table 3. For the thin wire bonding examinations, gold was selected as a reference material. For the investigations of wire-bond interconnections, test special devices were assembled and tested, Fig. 8. The general process flow of the investigations in this study is

- 1) Die Attachment

- → 3) Ageing and temperature cycling tests,

- → 5) Failure analysis.

- → 2) Wire bonding process development

- → 4) Tests at elevated temperatures, and

Table 3: Material properties of Au, Pt and Pd [13]

| Property                          | Au    | Pt    | Pd    |

|-----------------------------------|-------|-------|-------|

| α in ppm/K<br>0 to 300 °C         | 13.4  | 9.3   | 11.5  |

| Melting point in °C               | 1,063 | 1,769 | 1,552 |

| ρ in μΩcm at 20 ℃                 | 2.2   | 10.6  | 10.8  |

| Hardness HV<br>in kp/mm² at 20 ℃  | 25    | 55    | 50    |

| Hardness HV<br>in kp/mm² at 600 ℃ | 5     | 47    | 29    |

Table 4: Materials systems for the wire bonding process development

| Substrate                      | Test-<br>Chip | Metallisation                                    | Die attachment                                                   |

|--------------------------------|---------------|--------------------------------------------------|------------------------------------------------------------------|

| Al <sub>2</sub> O <sub>3</sub> | Si            | sputtered<br>10 nm Ti<br>20 nm TiW,<br>300 nm Pt | Al <sub>2</sub> O <sub>3</sub> -<br>based<br>ceramic<br>adhesive |

The specially fabricated test devices were the same for evaluating both the bonding on sensor chips and on the substrates. The test-chips were mounted with a ceramic adhesive with a high content of  $Al_2O_3$ , Table 4. Besides the ten bond pads the test-chips exhibit sensor structures for temperature and strain measurement using resistors.

Prior to the wire bonding, the bond pads were cleaned in order to increase the adhesion of the bonding wires [14, 15]. In this work  $O_2$ -plasma was well suited and the following results refer only to such a pretreatment. The Pt- and Pd- wire bonding was performed with a thermosonic process. All wires have diameters of 25  $\mu$ m and they were welded with a semi-automatic wedge-wedge bonder Delvotec 5430. The temperature of the parts was kept between 280 and 300 °C using a hot-chuck. For the other process parameters bonding force, ultrasonic power and time, a parameter optimization was performed. The optimized parameters of the thermosonic wedge-wedge bonding process for both 25  $\mu$ m wire materials Pt and Pd are: Bonding forces about 30 cN, ultrasonic powers of 0.9 to 1.0 W; welding times of 40 to 60 ms and a temperature of 300 °C.

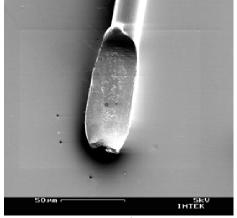

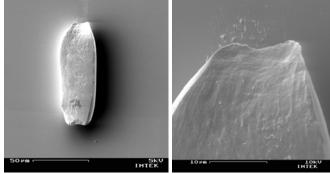

The loop pull-strength was taken as the principal mechanical criterion. Therefore a small hook is placed underneath the middle of the bond loop and pulls up the wire while the pull-force is recorded. For each parameter set at least 12 bond tests have been performed. Other variations include chip-to-chip bonding and chip-to-substrate bonding. Also a suited bonding tool geometry was found with a concave bond-tool, Figs. 8 and 9.

Fig. 8 Platinum bonded test device, assembled with high temperature stable packaging materials

Fig. 9 SEM image of 2<sup>nd</sup> bond-wedge on chip bond pad, with concave foot bond-tool

### Wire-pull test results and failure mode analysis

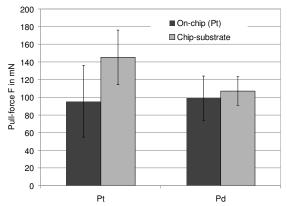

The data presented in this chapter consist of average values and  $2\sigma$ -error bars. The results for the pull-force of on-chip bonds directly after processing are presented in Fig. 10. The average pull strength of the untreated specimen with Pt and Pd wires is approximately 80 mN. After treating the devices with O<sub>2</sub>-plasma significantly higher mean values of 145 mN were measured for Pt. For Pd the average values were about 110 mN, Fig. 10. Generally the results for on-chip bonding were higher than for the chip-to-substrate loops. For the second type of interconnections we observed almost exclusive bond failure at the substrate side. A reason might be the higher surface roughness of the ceramic substrates which can reduce the adhesion of the sputtered metallization. After the pull testing the fracture surfaces were examined by microscope and SEM. Three basic failure modes of the bonds were observed:

### 1. Wedge lift-off

#### 2. Interface fracture

#### 3. Bond-neck failure

Fig. 10: Initial pull-test results for on-chip and chip-substrate bonds with 25  $\mu m$  Pt- and Pd-wires

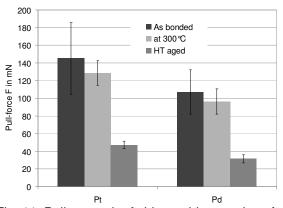

Fig. 11: Pull-strength of chip-to-chip samples after aging at 500 ℃ and during testing at 300 ℃

Fig. 12: Micrograph of interfacial fracture after initial bond pull-test of Pt-wire

Fig. 13: Wedge residue on chip metallization after pull-test of Pt-wire, detail on the right side (SEM)

Besides interfacial fracture the bond-neck break was the most common failure mode. In Fig. 12 the fractured bond interface after a pull-test is shown. Residues of the bond wedge are still sticking to the bond pad while parts of the metallization are lifted off. Fig. 13 exhibits the failure mode bond-neck break, which was observed when high pull strength values up to 200 mN were measured. This failure mode was found for both materials. The joint in Fig. 13 broke at the junction of wedge and wire, the so-called neck.

The following results of the wire-pull tests are presented for the Pt and Pd on-chip bonds, as here two identical bonding surfaces can be provided: On the as-bonded samples, pull-tests were performed on a heating chuck, with a constant temperature of 300 °C, to measure the stability of the bonds in a high-temperature environment. Fig. 11 exhibits the obtained results for the bond pull force. For Pt-bonded specimen treated with  $O_2$ -plasma the average values of the pull force measured at 300 °C were 140 mN, and for Pd 100 mN. The data are equivalent to a decrease of only 10 %, both for Pt and Pd, compared to the initial value. We assume that at 300 °C degradation is not yet activated thermally and that therefore the high strength of the wires can be exploited largely.

To investigate the long-term stability of Pt and Pd bonds, test devices were stored in a heating chamber at 500 ℃ in an air atmosphere for up to 200 hours in air. The pull force results for the aged specimen are presented in Fig. 11. We observed an average decrease of 70 % for all tested devices, compared to the initial pull-test results. The average pull force values of plasma-treated Pt wires were 45 mN and 32 mN for Pd bonds. When analyzing the degradation mode, the bond metallization of test devices showed degradation after 200 hours of aging at 500 ℃ in air. Consequently, the main failure mode observed after of the pull-tests was lift-off of the bond metallization. We expect that by an improved diffusion barrier system on the titanium adhesion layer will increase the pad adhesion and also the pull forces.

## 4. Discussion, conclusions and outlook

The investigations of this work revealed that the glass-soldering and the brazing process induce high stresses in the test-chips due to high process temperatures. In these cases is necessary to choose a substrate with a CTE close to silicon. AlN and  $Si_3N_4$  reduced the stress in glass-soldered test-chips by 50 %. Contrary to this ceramic adhesives and the siloxane resin induced low stresses in the chip. Stress levels were verified by optical measurements, simulation and analytical estimation. A second important criterion is the shear strength of the die attachments also after high-temperature operation. After aging for 100 h at 500 C both a glass solder and the ceramic adhesive C-A I were still sufficiently strong. Furthermore glass-solderings on  $Si_3N_4$ , and C-A I on AlN substrate increased in strength. Our further research will be focused on the influence of glass soldering, brazing and ceramic bonding on deposited SiC-layers. Another focus will be the processing and testing of the thin-film stress-sensors for high temperatures.

In this study Pt- and Pd-wire bonding was examined as interconnection technique for high temperature SiC-MEMS. The stability of the Pt bonds was higher and decreased only slightly after aging. So wire bonding is a reliable interconnection technology for SiC-MEMS in harsh environments. After a process optimization high stability was observed. The investigation of the bond fracture surface with a SEM revealed that the main bond-failure modes in pull testing are fracture of the bond interface and the bondneck for initial devices. This indicates an excellent adhesion of both materials on the bond metallization. After aging of bonded specimen for 200 hours at 500 °C in air, the electrical contact of the test structures was ensured but a decrease of the bond adhesion due to a degradation of the bond metallization was observed. The weakest link of the bond contacts changed from the bond-neck break for initial devices to the metallization lift-off. Average pull force values of 50 mN for Pt and 30 mN for Pd were measured after aging. Also first reliability results of the bond interconnection at 300 °C have been confirmed. For an increase of the long term stability of the platinum and palladium bonds, the optimization of the metal layers underneath the Pt bond is required. In further research, new test devices with different diffusion barriers will be investigated for longer times up to 1500 hours and with temperature shock cycles. Wire bonding will be conducted on pressure sensitive SiC structures to characterize the high temperature behavior of the sensors.

#### 5. References

- 1. D.J. Young, Jiangang Du, C.A. Zorman, W.H. Ko, Sensors Journal, IEEE, Vol. 4, 2004, pp. 464-470

- 2. A.A. Ned, R.S. Okojie, A.D. Kurtz, W.H. Ko, *Proc High Temperatur Electronics Conference*, June, 1998, pp. 257-260

- 3. M. Mehregany, C.A. Zorman, N. Rajan, C. H. Wu, Proc of the IEEE, August. 1998, pp. 1594-1609.

- 4. P. Hagler, P. Henson, R. W. Johnson, *IEEE Transactions on Industrial Electronics*, Vol. 58, No. 7, 2011, pp. 2673-2682

- 5. R.S. Okojie, V. Nguyen, E. Savrun, D. Lukco, *Proc* 16<sup>th</sup> Solid-State Sensors, Actuators and Microsystems Conf, Beijing, China, June. 2011, pp. 2875-225.

- 6. J. Freytag, I. Wennemuth, Proc Solid-State and Integrated Circuit Technology, 1998, pp. 219-221.

- 7. J.V. Mantese, W.V. Alcini, Journal of Electronic Materials, Vol. 17, No. 4 (1988), pp. 285-289.

- 8. R.K. Burla, C. Li, C.A. Zorman, M. Mehregany, IEEE Transactions on Advanced Packaging, Vol. 32, No. 2 (2009), pp. 564-574.

- 9. L. Coppola, D. Huff, F. Wang, R. Burgos, D. Boroyevich, Proc PE- Conference, 2007, pp. 2234-2240.

- R. Zeiser, P. Wagner, J. Wilde, Proc ECTC 2012, 62nd Electronic Components and Technology Conf, San Diego, CA, June 2012, pp. 338-343.

- 11. F. Bolger, C. Mooney, *IEEE Trans-CHMT*, Vol. 7, No. 4, 1984, pp. 394-398.

- 12. I. Y. Chien, M. N. Nguyen, *Proc 58<sup>th</sup> Electronic Components & Technology Conf*, Washington, FL, May. 1994, pp. 580-584.

- 13. DEGUSSA, Handbook for noble metals (in German), (Frankfurt am Main, 1967), pp. 34-36.

- 14. J. M. Nowful, S.C. Lok, S.-W. Ricky Lee, Electronic Materials and Packaging, Nov 2001, pp. 39-43.

- 15. W.H. Li, K. Reingruber, N. Mais, A. Acuesta, C. A. Yape, Proc Electronic Packaging Technology Conference, Singapore, Dec 2009, pp. 473-478.

### Acknowledgments

This study was funded by the German Federal Ministry of Education and Research, BMBF. The described investigations were part of the "Spitzencluster"-project SiC-Tech. The authors are very grateful for this support. Furthermore the authors want to thank all project partners for the good cooperation, especially the Robert Bosch GmbH.